이 페이지는 timing에 대한 일련의 페이지 에 속합니다. 이전 페이지에서는 timing 계산에 대한 이론을 설명하고 여러 timing constraints를 작성하는 방법을 보여주고 timing closure의 원리에 대해 논의했습니다. 이 페이지는 I/O timing constraints에 대한 토론을 시작합니다.

소개

지금까지 timing constraints 에 대한 전체 논의는 FPGA내부에 있는 paths 와 관련이 있었습니다. 드디어 FPGA의 I/O ports중 timing을 제어하는 constraints 에 대해 이야기할 시간입니다.

그러나 timing constraints에 대해 이야기하기 전에 FPGA 와 외부 구성 요소 간의 동기화를 위한 다양한 방법을 알아야 합니다. 이 주제를 고려하지 않고 작성된 Timing constraints는 가치가 없을 수 있습니다. 또한 I/O 인터페이스를 담당하는 logic이 제대로 작성되지 않을 수 있습니다. 극단적인 경우 PCB는 작동을 보장하는 I/O를 허용하는 데 필요한 배선이 부족할 수 있습니다.

외부 구성 요소와의 동기화에 대한 필수 인식을 통해 timing constraints에 대한 올바른 명령을 선택할 수 있습니다. 이에 대한 실질적인 측면은 다음 페이지 에 설명되어 있습니다.

이 페이지에서는 귀하가 IOB registers 에 대해 잘 알고 있다고 가정합니다.

Clock distribution

paths가 FPGA내부에 있는 한 path의 양쪽 사이에 있는 clock skew를 인식할 필요가 없었습니다. 도구는 clock의 배포를 담당했으며 timing 계산은 clock skew를 고려했습니다.

I/O timing constraints는 다릅니다. path 의 한쪽은 FPGA외부의 외부 구성 요소입니다. data signals와 동기화하기 위해 이 구성 요소는 pins중 하나에서 수신하는 clock 에 의존합니다. 그러나이 clock은 무엇과 동기화됩니까?

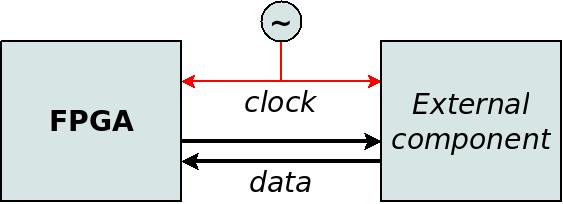

전략은 일반적으로 다음 두 가지 중 하나입니다.

- System synchronous clock: 외부 구성 요소는 FPGA의 clock input pin와 동일한 clock signal 에 연결됩니다. 이 전략은 common clock라고도 합니다.

- Source-synchronous clock: data signals와 함께 특별한 clock signal이 제공됩니다. 일반적으로 data signals는 clock와 동시에 값을 변경합니다. rising edge 또는 falling edge와 함께.

이 두 가지 전략은 다음에 자세히 설명합니다. source-synchronous clock 옵션의 경우 data signals가 inputs 와 outputs라면 상당한 차이가 있습니다. 따라서 이러한 시나리오는 별도로 논의됩니다.

System synchronous clock

PCB 에서 여러 구성 요소를 동기화하는 가장 간단한 방법은 모든 구성 요소를 하나의 clock에 연결하는 것입니다. 이를 system synchronous clock (또는 common clock )라고 합니다.

이 방법의 장점은 모든 구성 요소의 timing 매개변수가 하나의 clock signal에 상대적이라는 것입니다. 따라서 clock은 timing 계산을 위해 양쪽에서 동일합니다. 따라서 PCB의 두 구성 요소 간에 전파되는 data signal 의 경우 계산은 FPGA내부의 path 와 유사합니다. path는 첫 번째 clock edge에 상대적인 clock-to-output 로 시작합니다. path의 끝에서 tsu는 두 번째 clock edge에 상대적입니다. system synchronous 방식은 이 두 clock edges가 같은 clock에 속한다는 의미입니다.

따라서 system synchronous clock 로 작업하는 것은 간단하지만 이 방법은 상대적으로 낮은 주파수에만 적합합니다. 최소 clock period는 여러 timing 매개변수의 합계라는 timing 계산 소개를 상기하십시오. 첫 번째 flip-flop의 clock-to-output , 두 번째 flip-flop의 propagation delay 및 tsu . output port의 경우 clock-to-output은 PCB의 와이어가 필요한 전압에 도달하는 데 걸리는 시간이기 때문에 상대적으로 큽니다. 하지만 이것으로 끝나지 않습니다: clock skew 및 clock 와 관련된 기타 불확실성도 추가해야 합니다. 모든 수치를 종합하면 최소한의 clock period는 인상적이지 않을 수 있습니다.

일반적으로 system synchronous clock은 100 MHz보다 높은 data rate가 있는 I/O 에 적합하지 않습니다. 그러나 이것은 관련된 구성 요소에 따라 크게 달라집니다. 실제로 일부 전자 부품에는 훨씬 더 낮은 주파수에서도 system synchronous clock로 충족하기 매우 어려운 timing 요구 사항이 있습니다. 이러한 구성 요소는 PCB를 제조하기 전에 I/O timing을 계획하는 것이 중요한 이유 중 하나입니다.

set_input_delay 및 set_output_delay ( 다음 페이지 에서 설명)는 system synchronous clock와 함께 사용하기에 가장 적합한 timing constraints 입니다.

Source-synchronous clock

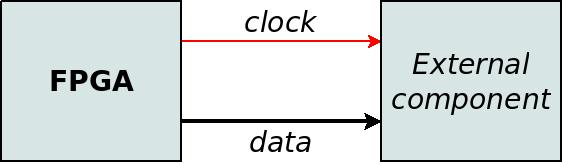

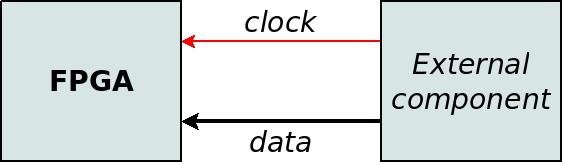

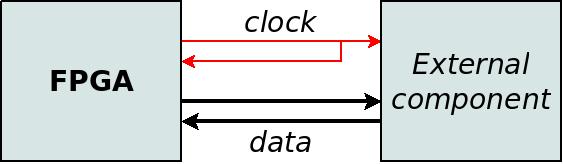

종종 PCB 의 두 구성 요소 간의 인터페이스는 이러한 구성 요소 중 하나에서 제공하는 clock을 기반으로 합니다. 당연히 clock이 FPGA 로 생성되는지 외부 구성 요소로 생성되는지는 차이가 있습니다.

따라서 네 가지 관련 시나리오가 있습니다.

- data 및 clock은 FPGA에서 생성된 outputs 입니다. 이 상대적으로 쉬운 시나리오는 source-synchronous outputs 에 대한 페이지에서 별도로 논의됩니다.

- data 및 clock은 외부 구성 요소에 의해 생성됩니다. 따라서 FPGA는 이를 input signals로 수신합니다. source-synchronous inputs 에 대한 페이지는 이 시나리오 전용입니다.

- clock은 FPGA에 의해 생성되지만 data는 양방향(또는 inputs)입니다. 이것은 source-synchronous inputs의 특별한 경우입니다. FPGA가 clock을 생성한다는 사실은 큰 차이를 만들지 않습니다. data inputs는 PCB에서 clock 와 동기화됩니다. 이 clock 에는 FPGA내부의 clock 와 관련하여 delay이 있습니다. 이 시나리오에 대한 자세한 내용은 source-synchronous outputs 관련 페이지를 참조하십시오.

- clock은 외부 구성 요소에 의해 생성되며 data는 양방향입니다. inputs ~ FPGA의 경우 data가 외부 구성 요소(source-synchronous clock)에 의해 생성되는 시나리오와 유사합니다. FPGA의 outputs는 외부 clock와 동기화되는 output 처럼 작동합니다. 따라서 이러한 outputs는 마치 system synchronous인 것처럼 배열됩니다.

Asynchronous inputs

일부 inputs는 clock와 연결되지 않습니다. 예를 들어 외부 구성 요소의 pushbuttons, I2C, RS232 및 다양한 status signals는 clock와 동기화되지 않습니다. 이러한 signals는 일반적으로 FPGA내부의 clock 보다 훨씬 느립니다. 따라서 일반적인 솔루션은 이러한 signals를 flip-flops (가급적 IOB registers )로 샘플링하고 일반 logic design 기술을 계속 사용하는 것입니다.

이러한 inputs는 샘플링에 사용되는 clock 와 동기화되지 않습니다. 따라서 IOB register (또는 port에 연결된 flip-flop )는 metastability guards 의 역할을 수행합니다. 따라서 unrelated clocks사이의 clock domain crossing 와 유사하게 각 port에 대해 두 번째 register를 사용해야 합니다. 그렇지 않으면 input signals가 느리고 현재 design이 제대로 작동하는 것처럼 보이더라도 예측할 수 없고 이상한 동작이 발생할 위험이 있습니다.

반복 가능한 동작을 보장하도록 timing constraints를 작성해야 합니다. flip-flops가 IOB내부에 배치되지 않은 경우에도 IOB registers 와 동일한 지침을 따라야 합니다. 추가 안전을 위해 이러한 registers의 metastability guards 역할과 관련하여 전용 timing constraint 도 추가하는 것이 좋습니다( 다른 페이지 에서 설명).

False paths

I/O ports 용False paths는 원칙적으로 FPGA내부 의 paths 와 동일합니다. set_false_path 명령은 특정 ports에 대해 timing 요구 사항이 적용되지 않도록 요청하는 데 사용됩니다.

False paths는 이미 FPGA내부에 있는 paths 에 대해 논의되었습니다 . 동일한 근거에 따라 I/O ports 에 대한 false paths 의 동기는 주로 unconstrained paths의 빈 목록을 유지하는 것입니다. 실수로 인해 port 에 timing constraints가 없는 경우 쉽게 식별할 수 있도록 이 목록은 비어 있어야 합니다.

False paths는 port 의 timing이 완전히 무의미한 경우에만 사용해야 합니다. 예를 들어 LEDs 및 DIP switches를 사용합니다.

SDC constraints의 예:

set_false_path -to [get_ports led_0] set_false_path -from [get_ports dip_switch_0]

요약

이 페이지에서는 FPGA 와 외부 구성 요소 간의 동기화를 위한 몇 가지 전략을 설명했습니다. 선택한 전략은 logic design 와 timing constraints에 영향을 미칩니다.

이 지식을 바탕으로 I/O timing constraints를 작성하는 방법에 대해 논의할 시간입니다.